Séptima Practica:

Introducción:

Para esta séptima practica de laboratorio haremos uso del simulador CircuitVerse y de los Mapas de Karnaugh, haremos uso de sumadores, multiplexores, comparadores y diferentes configuraciones para poder visualizar la suma de dos números BCD en el display de 7 segmentos, también es evidente que se hará el uso de las tablas de verdad, Algebra de Boole y leyes de Morgan. Con los comparadores, sumadores y multiplexores mostraremos el funcionamiento que es necesario para llevar a cabo la suma de dos números BCD y con los Mapas de Karnaugh la forma de visualizar estos números.

Sistema BCD:

Es un sistema numérico usado en sistemas computacionales y electrónicos para codificar números enteros positivos y facilitar las operaciones aritméticas. Es un código ponderado porque cada posición representa un peso específico (8421). En BCD cada cifra que representa un dígito decimal (0, 1,…8 y 9) se representa con su equivalente binario en cuatro bits ya que son la cantidad de bits necesarios para representar el 9, el numero mas alto que se puede representar en un numero BCD. Esto quiere decir que para números de más de una cifra hacen falta dos números BCD para componerlo ya que como se muestra con el BCD sólo se utilizan 10 de las 16 posibles combinaciones que se pueden formar con números de 4 bits, por lo que el sistema pierde capacidad de representación, aunque se facilita la compresión de los números. Esto es porque el BCD sólo se usa para representar cifras no números en su totalidad.

Una forma sencilla de calcular números en BCD, es sumando normalmente bit a bit, y si el conjunto de 4 bits sobrepasa el número 9, entonces se le suma un 6 (0110) en binario, para poder volver a empezar, como si hiciéramos un módulo al elemento sumante.

Una forma sencilla de calcular números en BCD, es sumando normalmente bit a bit, y si el conjunto de 4 bits sobrepasa el número 9, entonces se le suma un 6 (0110) en binario, para poder volver a empezar, como si hiciéramos un módulo al elemento sumante.

Comparadores:

Un circuito comparador tiene la función de comparar dos números A y B de N numero de bits tomadas como un número entero sin signo e indica si son iguales o si una es mayor que otra en tres salidas A = B, A > B, A < B. También aclarar que evidentemente por combinación solo puede haber una salida en estado alto y las demás en estado bajo.

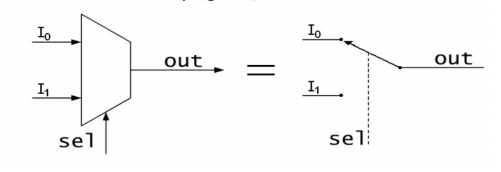

Multiplexores:

Es un circuito digital que selecciona una de entre varias entradas de datos In y transporta su valor a la salida del circuito. La selección de los datos se realiza mediante una o varias entradas de control llamadas selectores. Estas se calculan utilizando la siguiente fórmula: Número de canales de entrada dividido sobre el numero de entradas=2^n, en el cual n sera el numero de selectores necesarios para el correcto funcionamiento de el multiplexor.

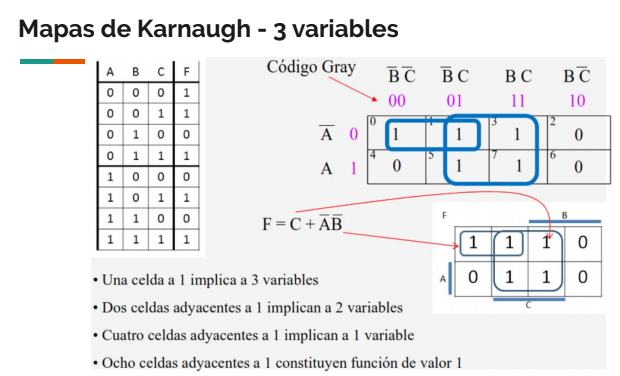

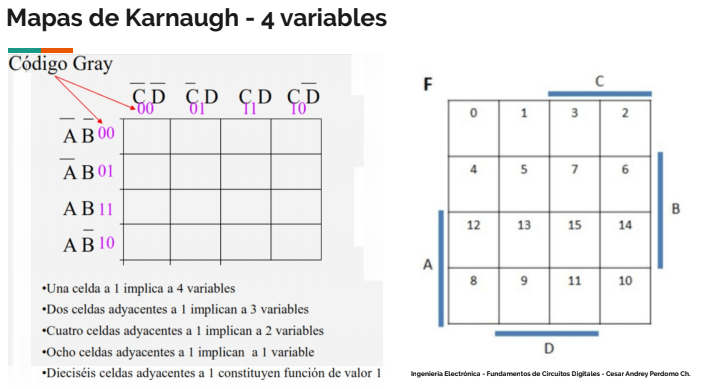

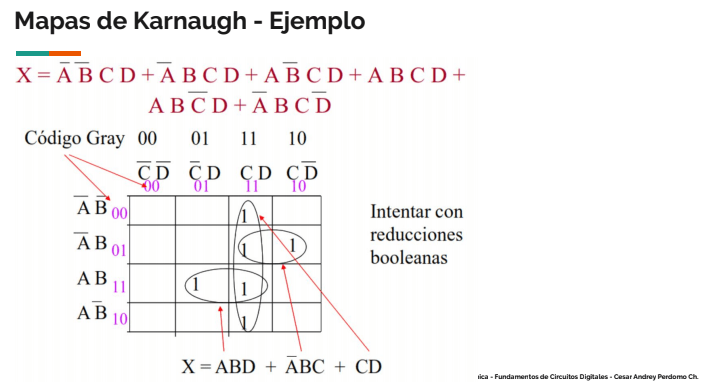

Mapas de karnaugh:

Son una herramienta muy utilizada para la simplificación de circuitos lógicos. Cuando se tiene una función lógica con su tabla de verdad y se desea implementar esa función de la manera más económica posible se utiliza este método.

Condiciones No Importa:

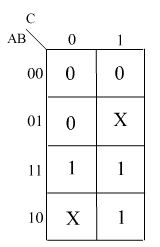

En muchos circuitos lógicos hay condiciones de entrada para las que no se especifican los niveles de salida, en la mayoría de los casos es por que estas condiciones nunca se presentaran o simplemente el nivel lógico de la salida es irrelevante.

Colocaremos una X que representa la condición no importa. La persona que este realizando la simplificación tiene la libertad de determinar el nivel lógico para la salida de la condición “no importa”, con el fin de producir la expresión mas simple.

Metodología:

1. Materiales:

– 2 Sumadores de 4 bits.

– 1 comparador de 5 bits.

– 1 MUX de 8 a 4.

– 1 decodificador de BCD a 7 segmentos.

– 2 Display’s de 7 segmentos.

– 8 entradas.

– 8 salidas.

– 2 Display Enable.

– 1 one hot de 2 bits con un clock de entrada.

Procedimiento:

En esta practica el montaje se diseño a partir de pasos y de esquemas que se fueron uniendo para lograr el objetivo de la practica. La suma en código BCD utiliza las mismas reglas de la suma binaria. Si una suma de dos números es menor o igual que 9, el número BCD resultante es válido. Si la suma es mayor que 9, o si se genera un acarreo el resultado no es válido. En este caso, se suma el número binario 0110 para pasar de nuevo al código BCD. Si se genera acarreo al sumar 0110, éste se suma al siguiente grupo de 4 bits. En los siguientes ejemplos se verán los casos que se pueden presentar.

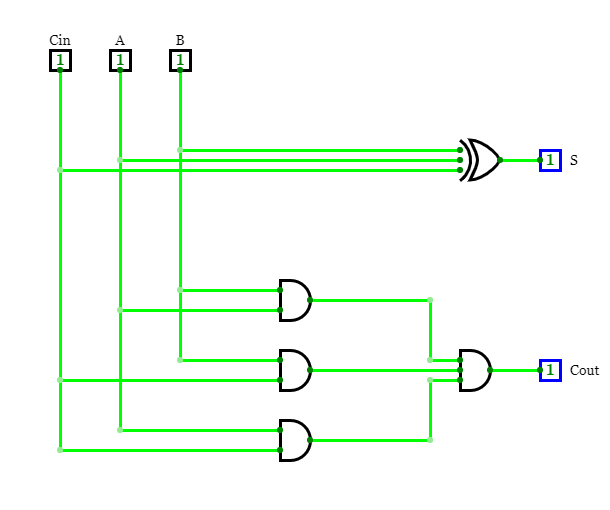

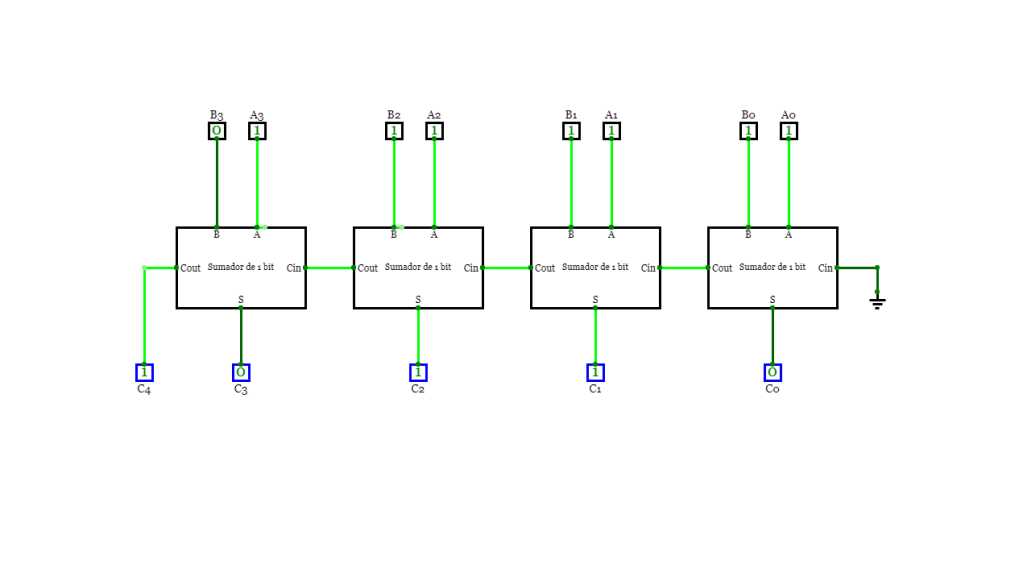

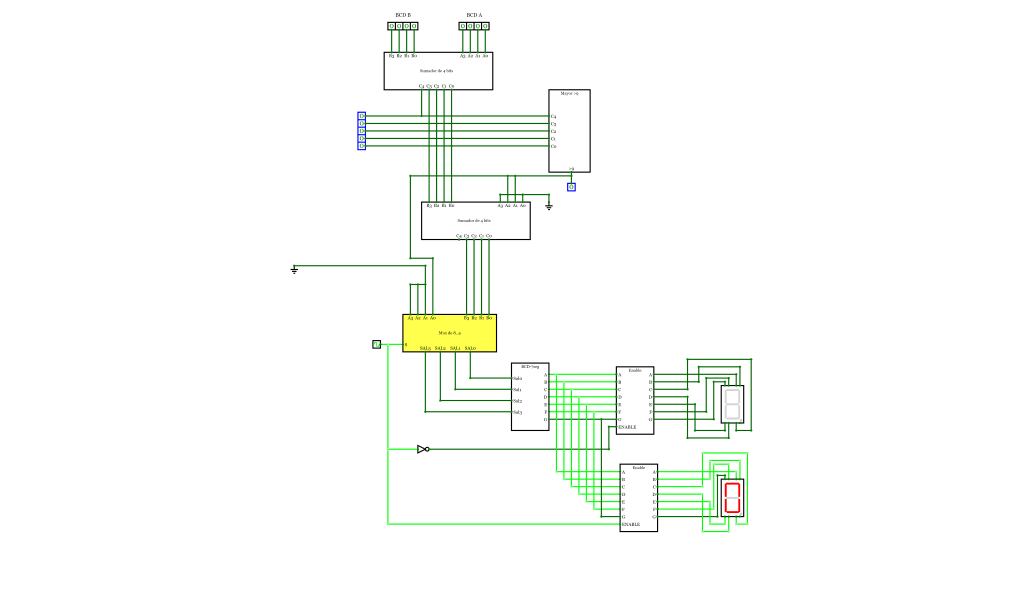

Por lo tanto primero haremos el sumador de los dos números BCD, por lo que se hace necesario hacer un sumador de 4 bits. La construcción del mismo se hizo a partir de sumadores de 1 bit llamados sumadores completos de un bit ya que al contrario del otro tipo de sumador a este se le puede integrar un acarreo de entrada por lo que tendremos dos circuitos:

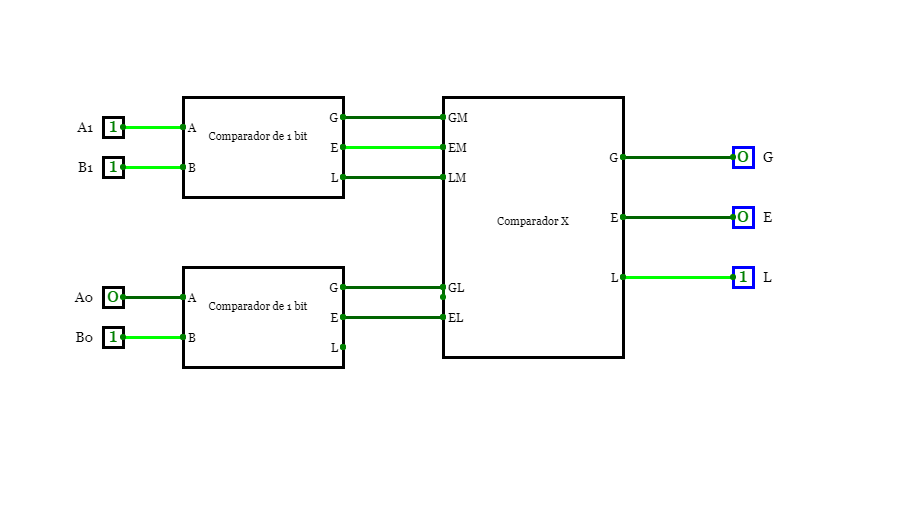

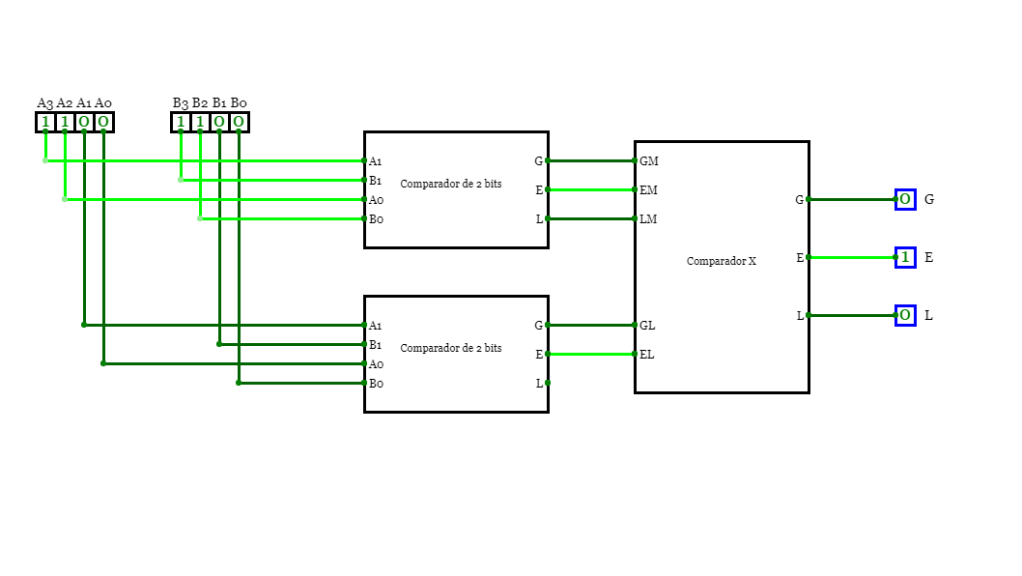

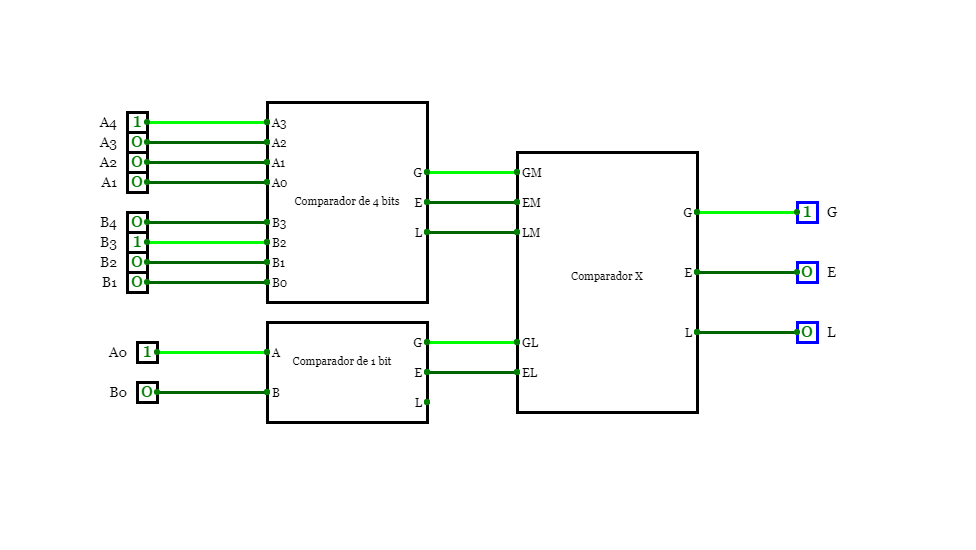

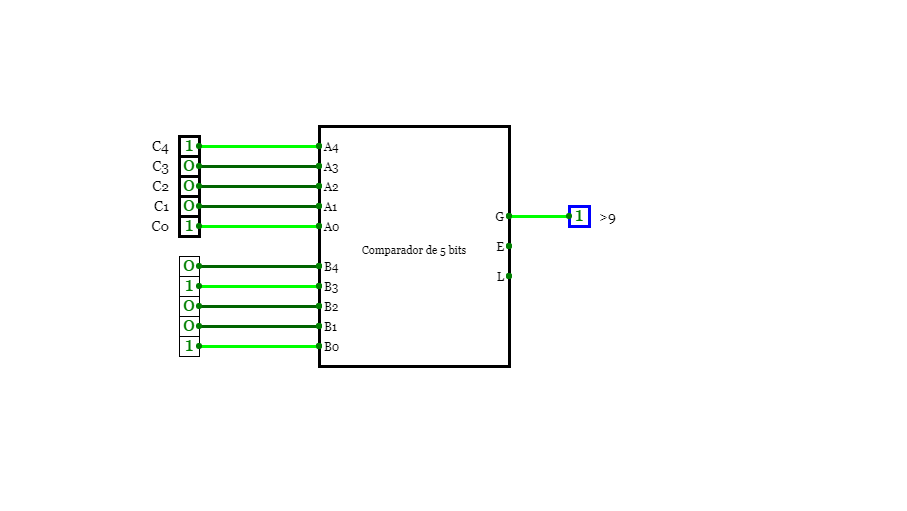

Después nos disponemos a crear un circuito para el cual determine cuando la suma sea mayor al numero 9 o se genere un acarreo no valido se sume el numero 6 para construir el siguiente numero BCD, el cual es necesario para expresar la suma. Para esto se utilizara un comparador de 5 variables el cual comparara el resultado de la suma BCD y el numero 9 en binario y de esta forma determine que resultados en la suma es mayor al 9. Este comparador lo construiremos a partir de el comparador de 1 bit y el comparador general dado en clase, el cual interconectaremos con los comparadores de 1 bit y obtener el comparador de 5 bits.

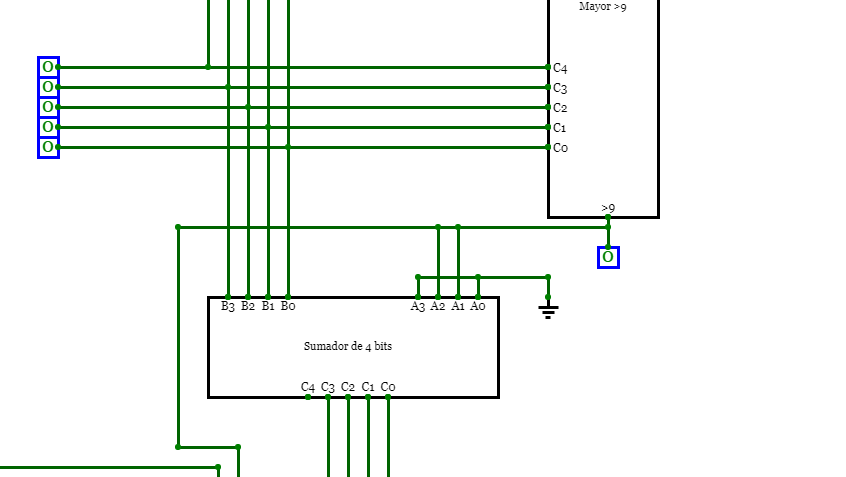

Después falta crear un mecanismo que nos sume el numero 6 cada vez que la suma BCD sea mayor que 9 o contenga un acarreo. Eso lo haremos con otro sumador de 4 bits el cual tendrá 2 entradas de 4 bits en el cual en los primeros 4 tendremos la suma BCD obtenida del sumador anterior y en la otra el numero 6 solo en caso de ser mayor que 9 o 0 en caso de tener un numero menor de 9, por lo que adaptaremos la salida del circuito mayor que 9 a una de las entradas de 4 bits de forma que cuando obtengamos un numero mayor a 9, en la salida del circuito «mayor que 9» obtendremos un 1 y cuando no lo sea obtengamos un 0 por lo que lo conectamos de la siguiente manera:

Como se puede observar se acoplo la salida del comparador de 5 bits de modo que en el caso en el que la suma nos de mayor que 9 nos sume en el sumador de 4 bits el numero 6 (0110) y en caso contrario nos sume un 0.

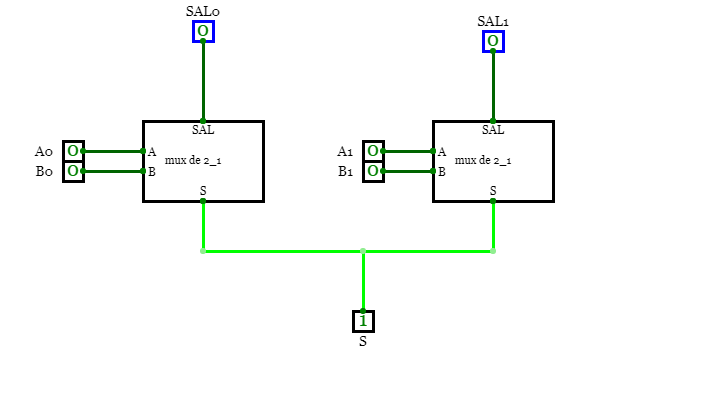

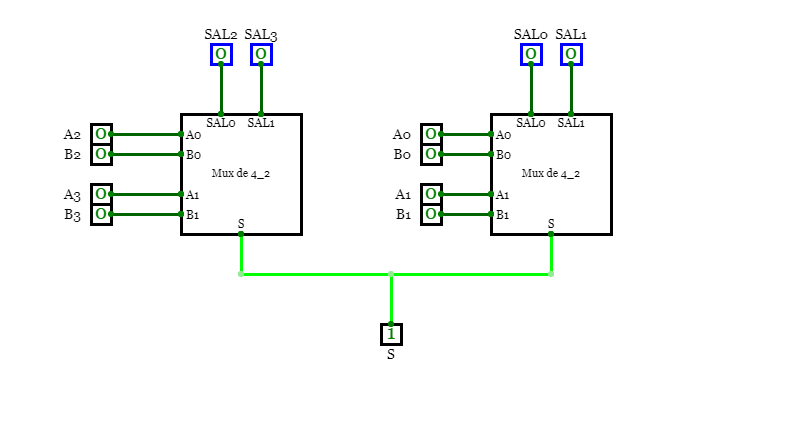

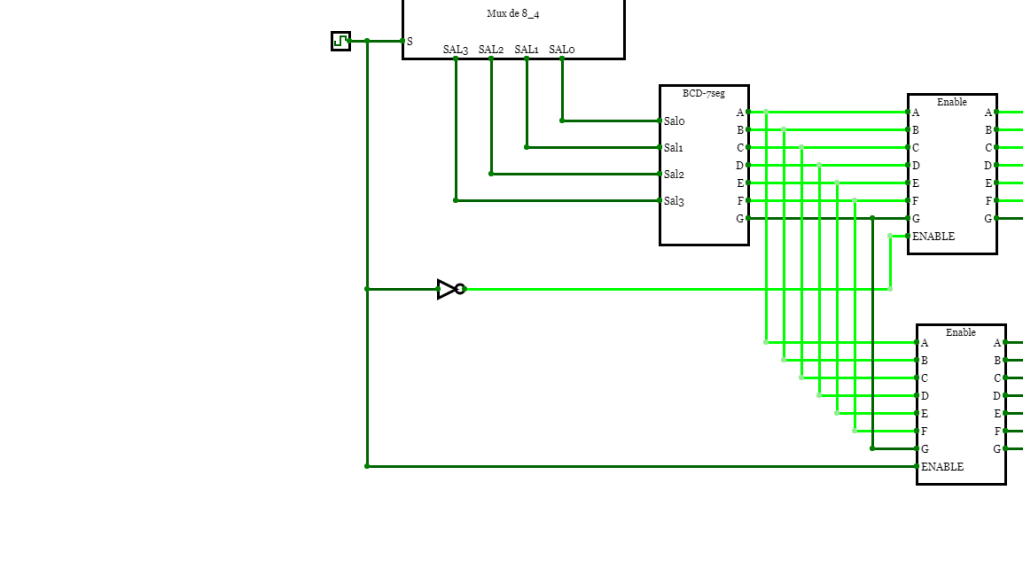

Ya solo queda poder visualizar nuestro dos números BCD resultantes de la suma en diferentes display de 7 segmentos, por lo que haremos uso de un multiplexor de 8 a 4 el cual tendrá de entrada el resultado de la suma BCD y de entrada en el selector tendrá un clock el cual lo usaremos para hacer la ilusión en la que los display se enciendan al tiempo y se visualice de una manera mas cómoda el resultado de la suma. Para diseñar el multiplexor usaremos primero el multiplexor de 2 a 1 y de esta manera poder interconectarlos para crear el multiplexor de 4 a 2 y por ultimo de 8 a 4.

La forma de ir interconectando estos multiplexores serán conectándolos por medio de sus selectores y conectarlos a un selector nuevo en cada montaje.

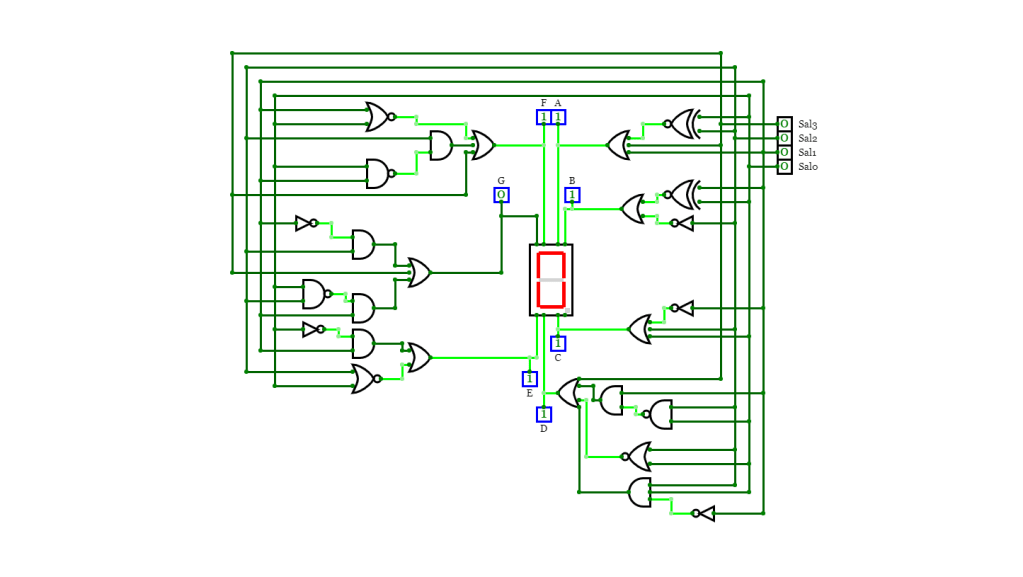

Después ya solo queda mostrarlos en los respectivos display por medio del decodificador que convertirá el numero BCD de forma que se muestre en el display 7 segmentos. Esto lo haremos por medio de la tabla de verdad y los Mapas de Karnaugh obteniendo el siguiente circuito:

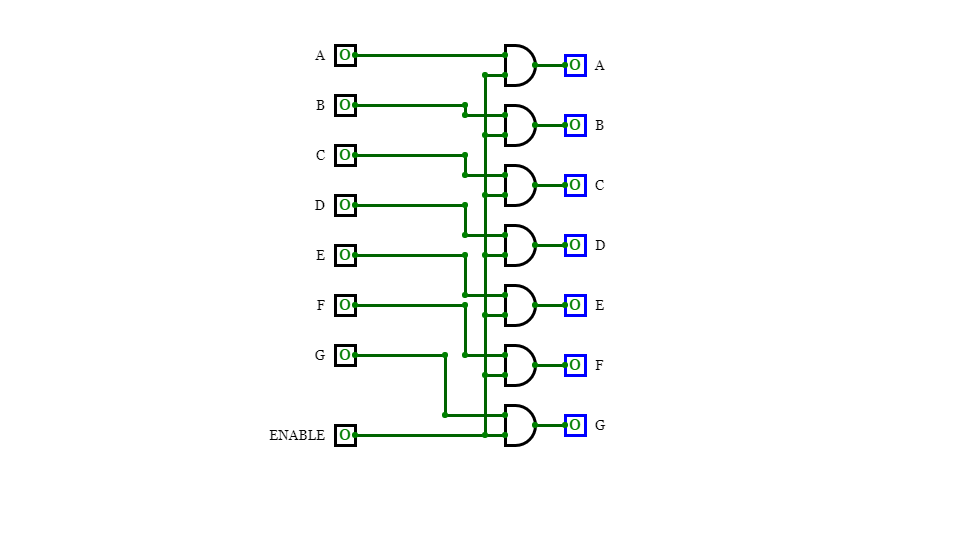

A estos displays agregaremos lo que se conoce como un one hot, el cual al tener de entrada el clock a la salida lo que se obtendrá sera una variación que estará cambiando de salidas de (0,1) a (1,0) en un plazo de tiempo muy corto, esto para la finalidad de activar un display y apagar el otro para visualizar correctamente los resultados de la suma, pero para prender y apagar los display se necesita hacer uso de dos enables controlados por el one hot.

Por ultimo el circuito completo quedaría de la siguiente forma:

Análisis de Resultados:

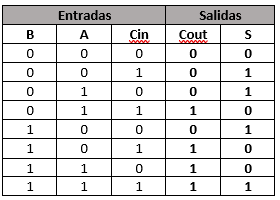

Primero observaremos la tabla usada para el sumador de 1 bit con acarreo de entrada:

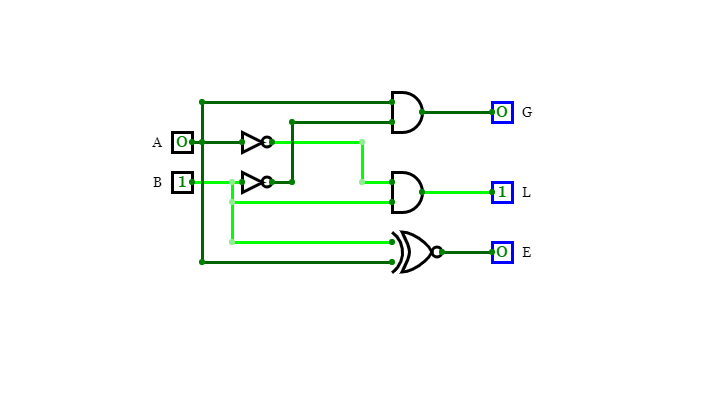

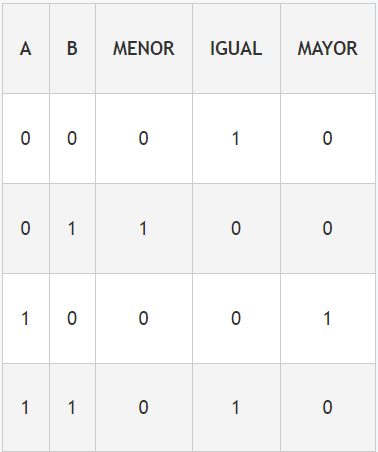

Después la creación del comparador de 1 bit:

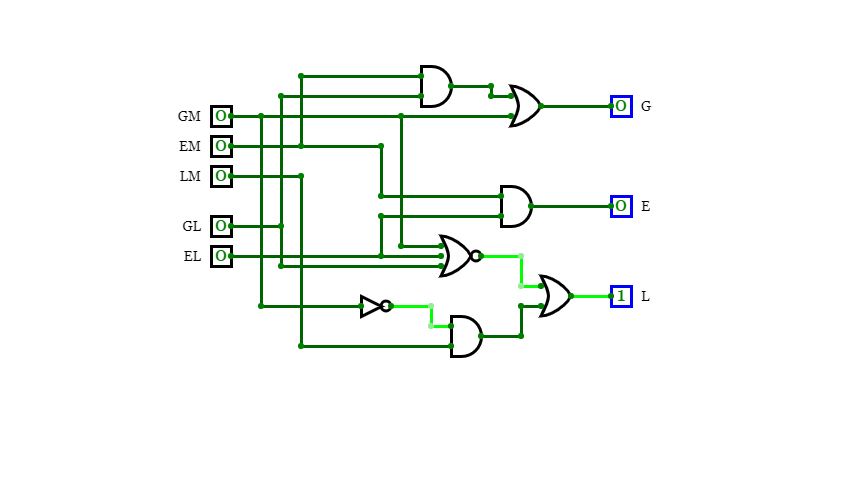

Para la creación del comparador general se usaron los Mapas de Karnaugh y de esta manera calcular la ecuación del mismo. Como por cada salida del circuito es necesario aplicarle el método de Mapas de Karnaugh, vamos a obtener 3 Mapas uno para (A = B), (A < B) y (A > B).

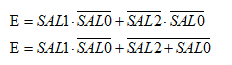

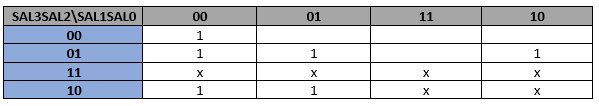

– Para el segmento E (A = B) tenemos:

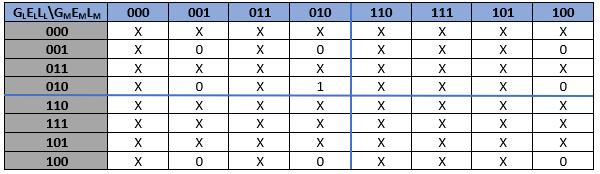

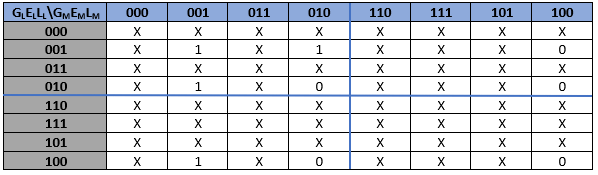

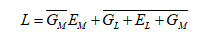

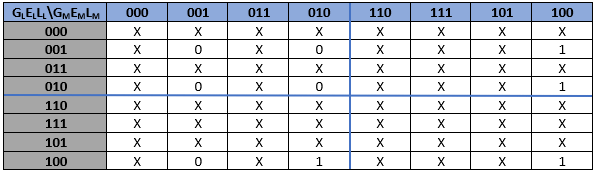

– Para el segmento L (A < B) tenemos:

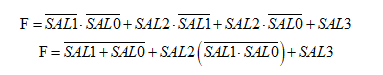

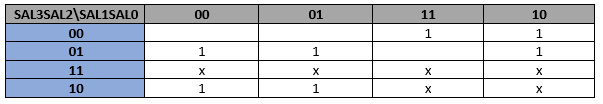

– Para el segmento G (A > B) tenemos:

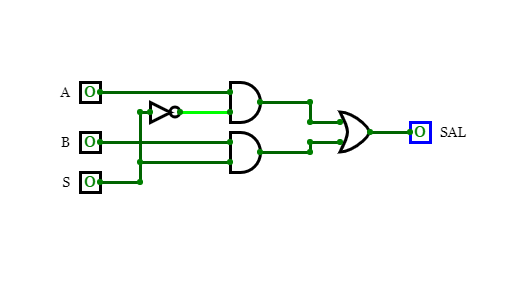

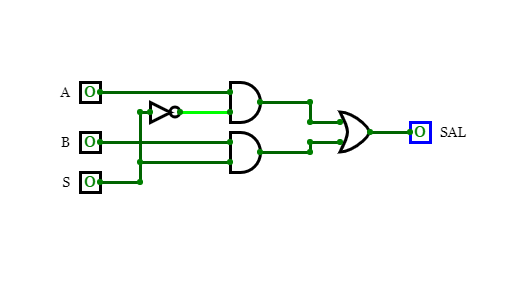

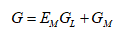

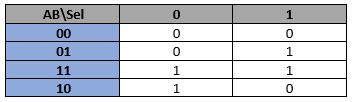

Ahora por medio del Mapa de Karnaugh dado en clase se obtiene el circuito del MUX de 2 a 1:

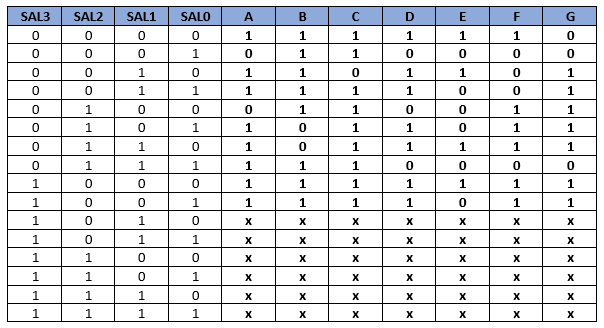

Ahora se realizara la tabla de verdad para la decodificación de los números BCD y poderlos visualizar en los display de 7 segmentos.

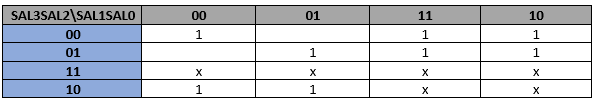

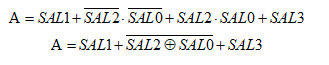

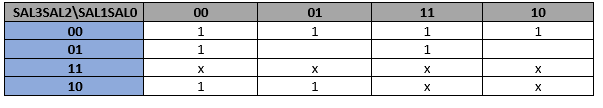

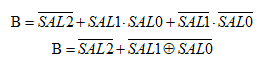

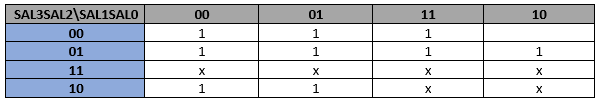

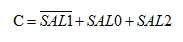

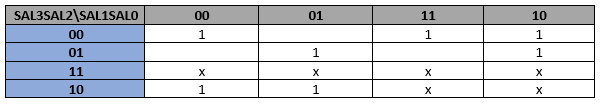

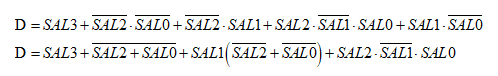

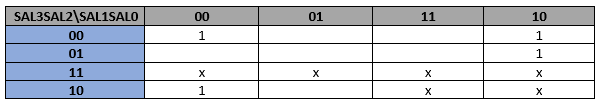

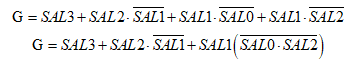

La ecuaciones que describen el funcionamiento de cada segmento las hallaremos por medio de Mapas de Karnaugh:

Segmento A:

Segmento B:

Segmento C:

Segmento D:

Segmento E:

Segmento F:

Segmento G:

Conclusiones: