Décima Práctica:

Introducción:

Para esta décima práctica de laboratorio haremos uso del simulador CircuitVerse, el circuito 74LS185, mapas de Karnaugh al igual que de las compuertas universales NAND y NOR. Utilizaremos estas herramientas para diseñar multiplexores, comparadores, bloques de memoria y varios displays donde se visualizará la finalidad de la práctica mostrando el camino de datos el cual implementaremos por medio de las memorias latch SR y de un sumador/restador.

LATCH:

El latch (cerrojo) es un tipo de dispositivo de almacenamiento temporal de dos estados (biestable), asimismo los latches se pueden agrupar de tal manera que logren almacenar más de 1 bit, por ejemplo el ‘latch quad ‘ (capaz de almacenar cuatro bits) y el ‘latch octal’ (capaz de almacenar ocho bits). Los latches son dispositivos biestables asíncronos que no tienen entrada de reloj los latches son similares a los flip-flops, ya que son también dispositivos de dos estados que pueden permanecer en cualquiera de sus dos estados gracias a su capacidad de realimentación, lo que consiste en conectar (realimentar) cada una de las salidas a la entrada opuesta. La diferencia principal entre ambos tipos de dispositivos está en el método empleado para cambiar de estado.

LATCH SR:

Un latch es un tipo de dispositivo lógico biestable o multivibrador. Un latch S-R (Set-Reset) con entrada activa a nivel ALTO se compone de dos compuertas NOR acopladas, tal como se muestra en la Figura (1); un latch con entrada activa a nivel BAJO está formado por dos compuertas NAND conectadas. Observe que la salida de cada compuerta se conecta a la entrada de la compuerta opuesta.

COMPUERTAS UNIVERSALES NAND Y NOR:

Los circuitos combinacionales se construyen mas a menudo con compuertas NAND o NOR, debido a que son mas comunes desde el punto de vista de hardware en la forma de circuitos integrados.

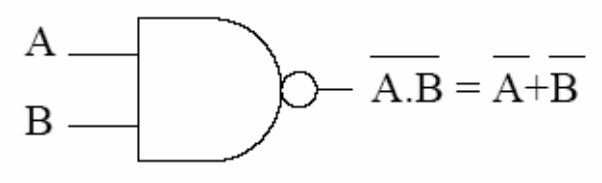

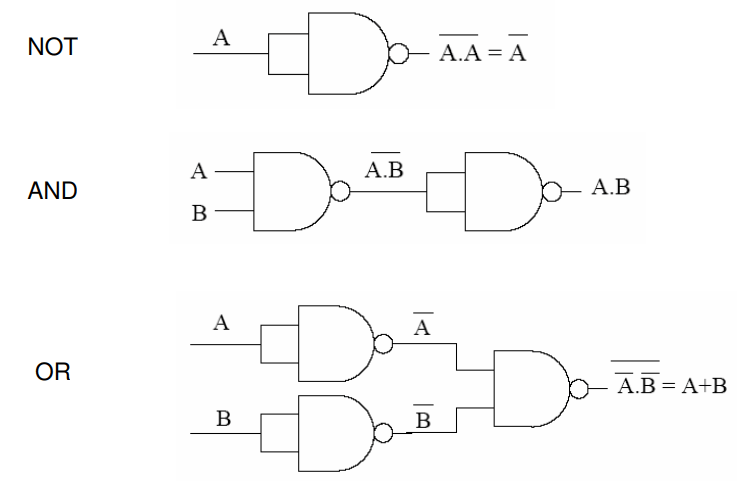

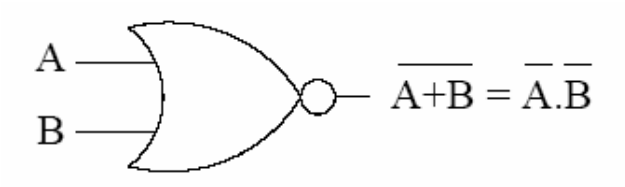

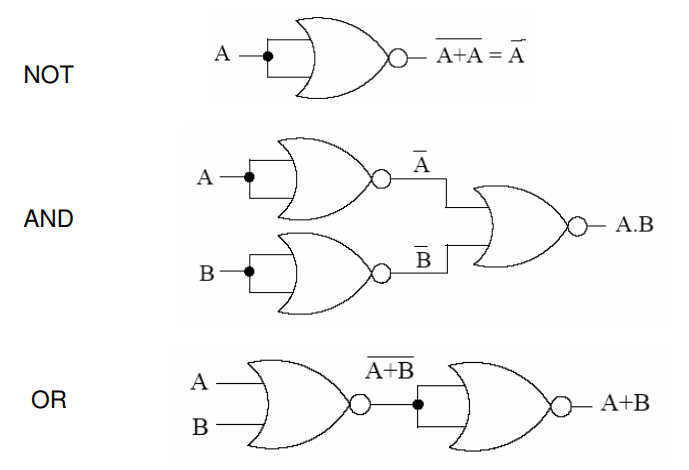

La compuerta NAND y NOR son compuertas universales ya que cualquier sistema digital puede implementarse por medio de ellas.

NAND:

NOR:

LUT:

Una LUT , que significa LookUp Table , en términos generales es básicamente una tabla que determina cuál es el resultado para cualquier entrada (s) dada. En el contexto de la lógica combinacional, es la tabla de verdad . Esta tabla de verdad define efectivamente cómo se comporta su lógica combinatoria. En otras palabras, cualquier comportamiento que se obtiene al interconectar cualquier número de puertas (como AND, NOR, etc.), sin rutas de retroalimentación (para asegurar que no tenga estado), puede implementarse mediante una LUT.

74LS185:

Es un integrado el cual nos permitirá convertir de manera sencilla un número binario a un número a BCD, ya que por la finalidad de la práctica es necesario convertir 6 bits a BCD pues la manera más eficaz de poder hacer esta conversión es por eso que usaremos el 74LS185, ya que para esto implementaremos el LUT en nuestra práctica por lo que el diseño de este circuito sera por medio de su tabla de verdad .

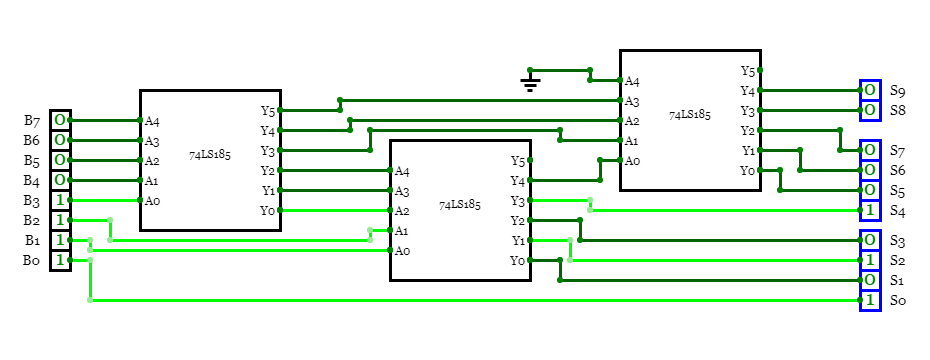

Pero para poder convertir 6 bits se hará uso de un montaje especifico el cual encontraremos en el datasheet del mismo por lo que se hará uso de la siguiente conexión con los integrados 74LS185

Metodologia:

Materiales:

– 12 entradas.

– 1 comparador de 6 bits.

– 1 sumador de 6 bits.

– 2 Memorias de 6 bits implementando el latch SR.

– 2 Mux de 12 a 6.

– 1 circuito con complemento a 2.

– 3 convertidores de binario a BCD de 7 bits.

– 1 decodificador de BCD a 7 segmentos.

– 5 display’s de 7 segmentos.

– 1 contador de 2 bits proporcionado por el docente.

Procedimiento:

En esta práctica el montaje se diseñó a partir de pasos y de esquemas que se fueron uniendo para lograr el objetivo de la práctica. Haremos como lo dice la práctica un camino de datos por medio de las memorias latch SR, el sumador/restador de 6 bits y el comparador de 6 bits. Por lo que primero empezaremos será construyendo las memorias de 6 bits por medio de los latch SR.

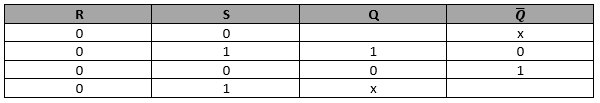

Tabla de verdad del latch SR:

Como este circuito ya viene implementado en el circuito por medio de un encapsulado como se observa en la «figura 9» lo único que hacemos son las conexiones necesarias y el uso de las memorias latch SR necesarias para construir las 2 memorias de 6 bits.

Después de tener implementado las dos memorias de 6 bits procedemos a diseñar el comparador de 6 bits, esto con el objetivo de poder realizar la operación resta en nuestro circuito, ya que solo nos va a interesar la salida A < B.

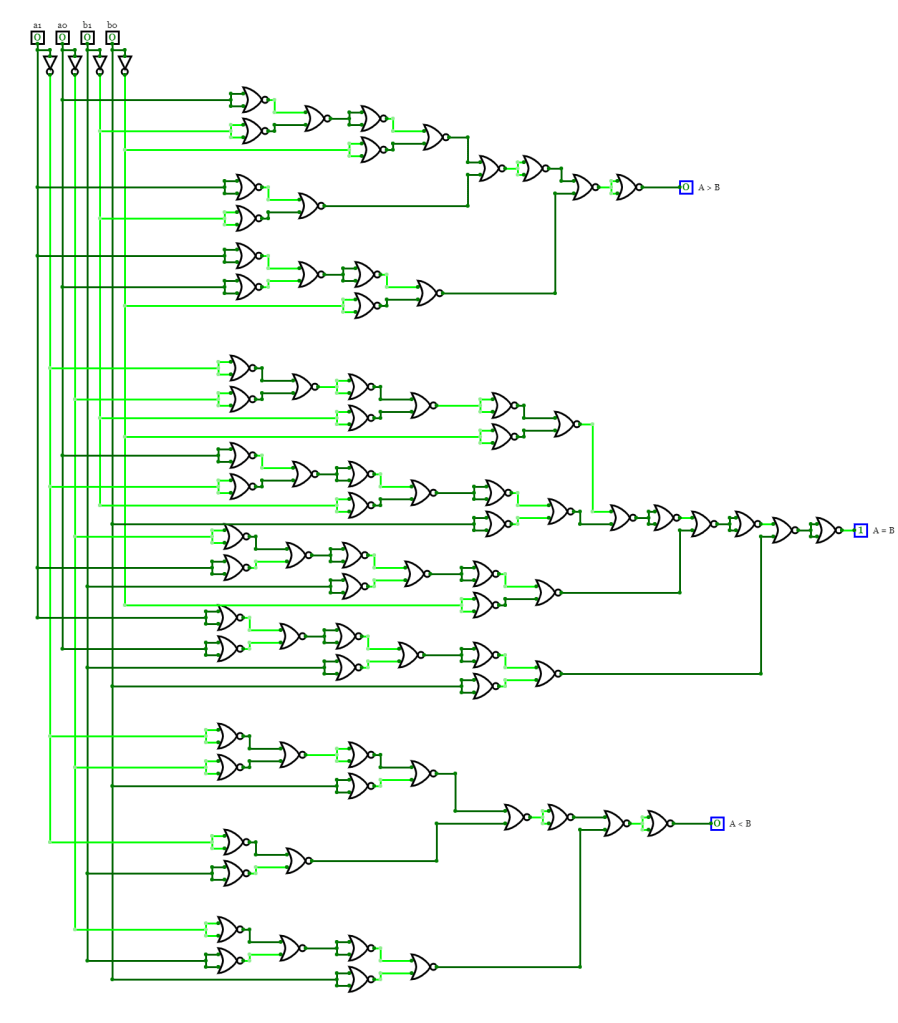

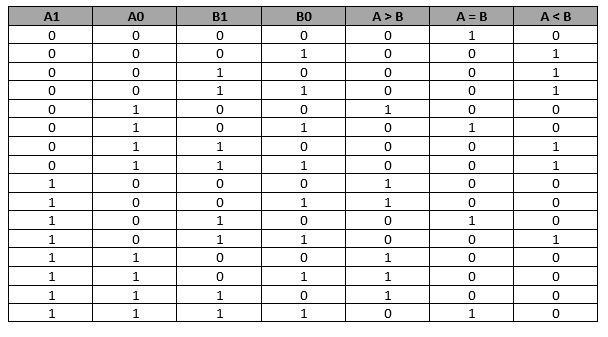

Comparador de 2 bits con compuertas NOR:

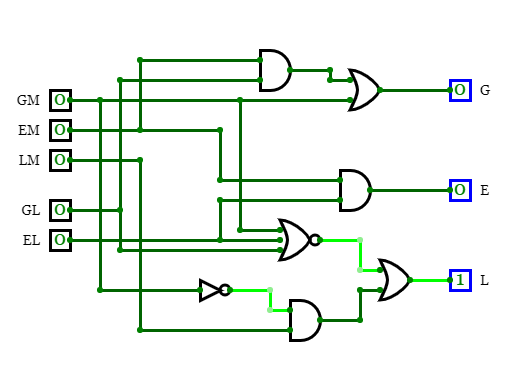

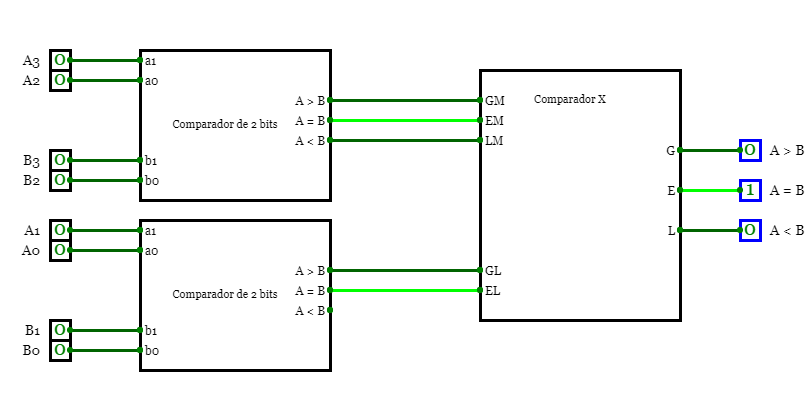

Después de tener diseñado el comparador de 2 bits, realizamos el comparador general el cual sera de gran uso para diseñar el comparador de 4 bits y paso siguiente el de 6 bits.

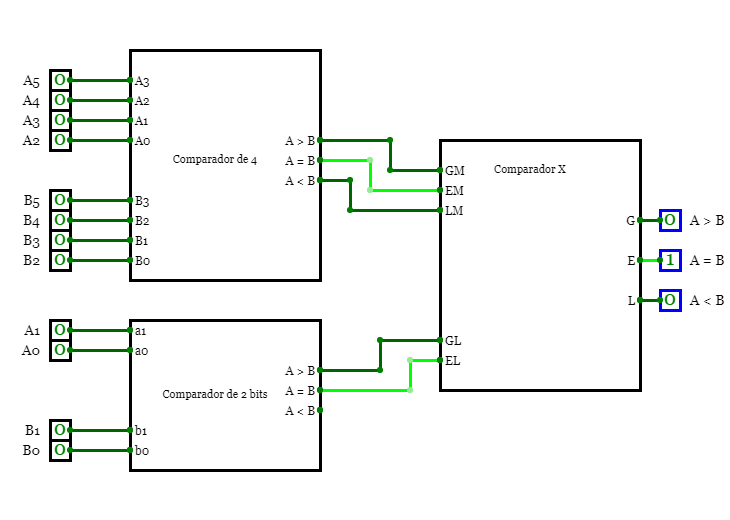

Teniendo diseñando el comparador de 2 bits, realizamos el comparador de 4 bits:

Ahora con el comparador de 4 bits y 2 bits realizamos el comparador de 6 bits:

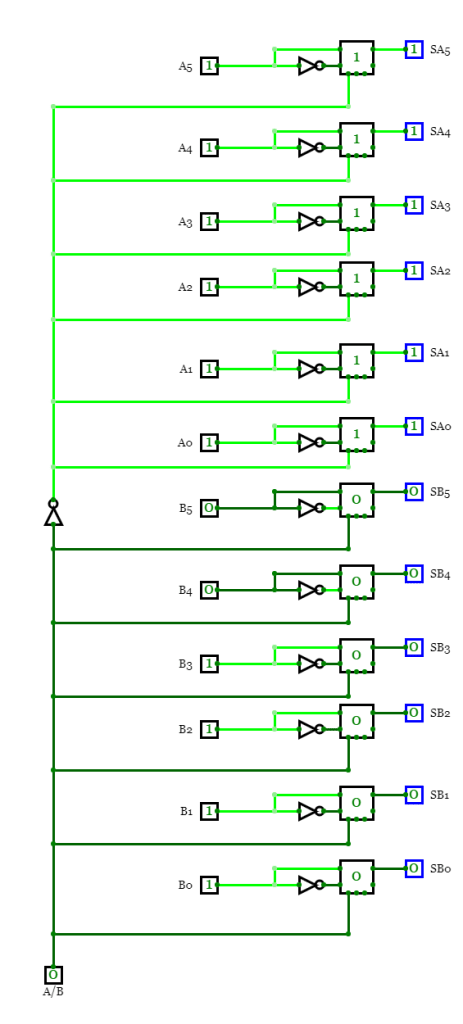

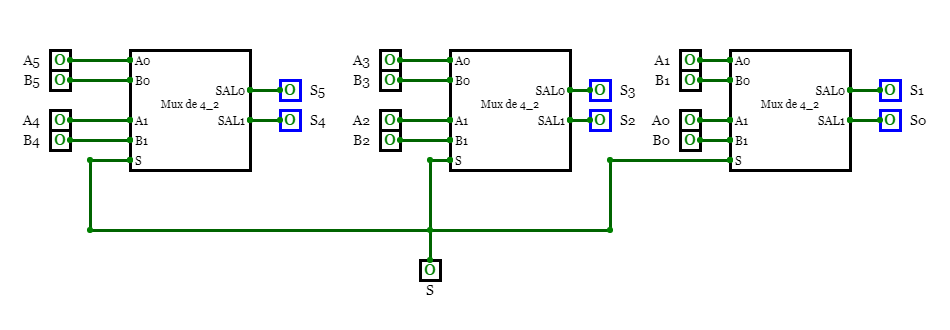

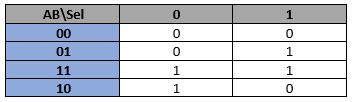

Después diseñamos los multiplexores de 12 a 6 ya que para generar la resta cuando A < B tendremos que cambiar los selectores del multiplexor para poder generar la resta y poder observar la resta con números negativos.

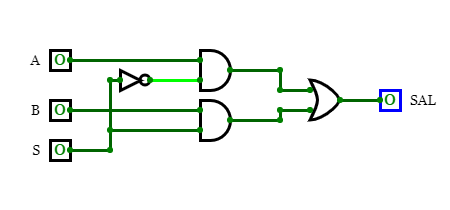

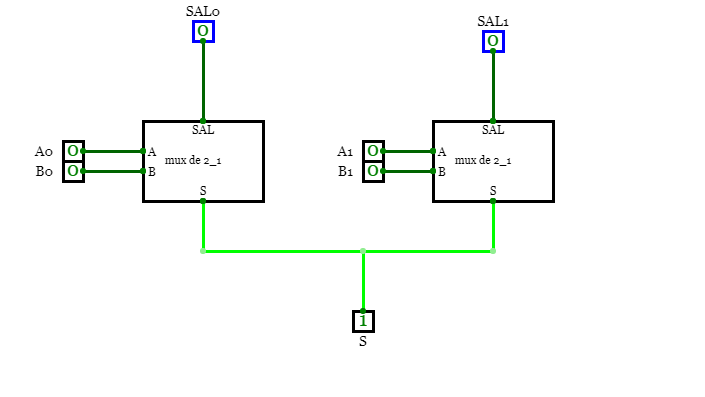

Partimos de diseñar el MUX de 2 a 1:

Después diseñamos el MUX de 4 a 2:

Luego el MUX de 12 a 6:

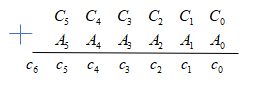

Para poder hacer la operación resta a partir de un sumador se hará este proceso por medio del complemento a 2, por lo que el circuito que realice dicha acción tendrá que hacer lo siguiente:

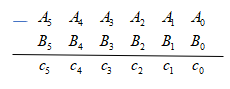

La operación resta:

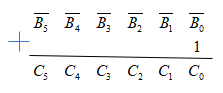

Ahora lo que haremos sera negar el numero B y sumarle 1:

Dándonos como resultado un nuevo número el cual sumaremos con el numero A y de este modo realizaremos la operación resta

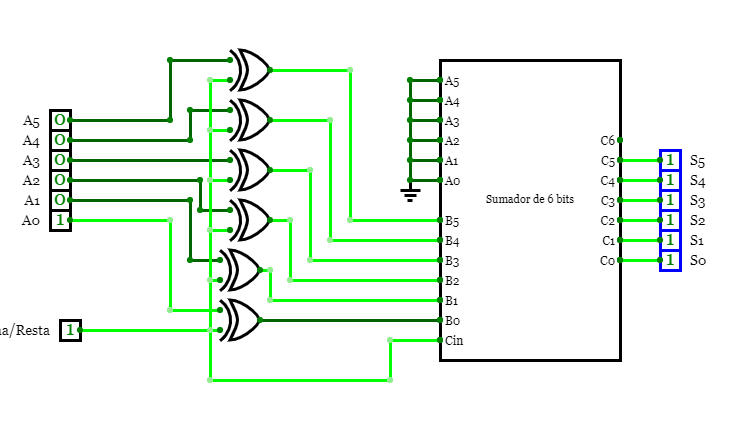

Por lo que diseñaremos un circuito que cumpla el complemento a 2 para restar:

Como se observa si esta en 1 el bit de Suma/Resta el complemento a 2 funcionará, en caso de que no a la salida tendremos el mismo numero en cual sumaremos con un sumador de 6 bits que diseñaremos a partir de un sumador completo de 1 bit.

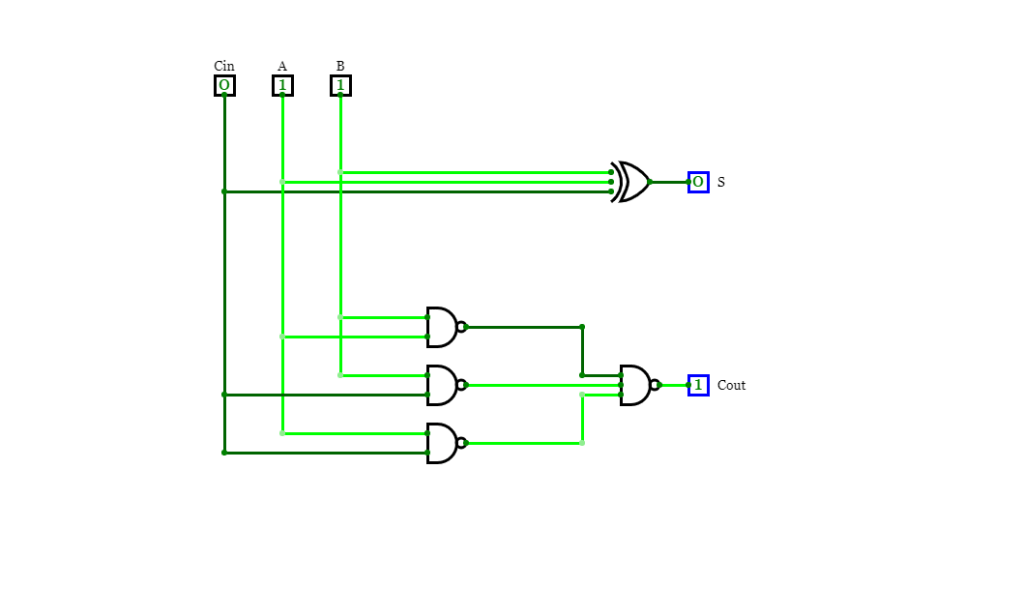

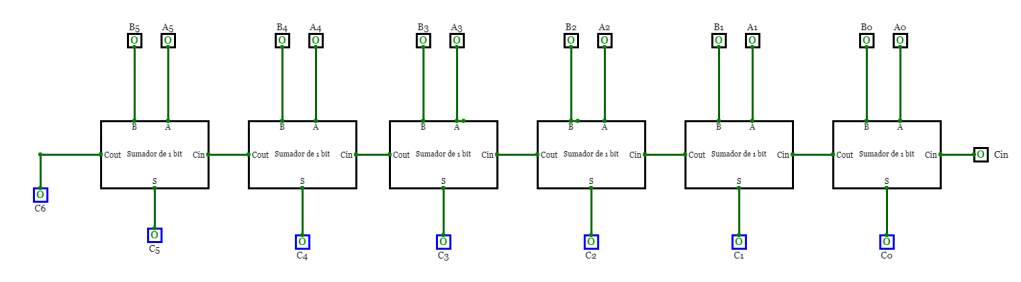

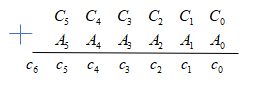

Sumador de 6 bits:

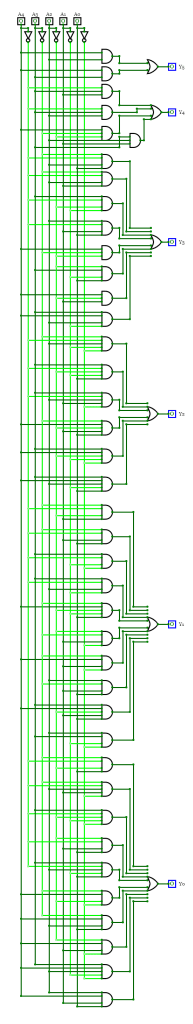

Después diseñamos por medio del circuito 74LS185 el convertidor de 7 bits de binario a BCD. Primero diseñamos el circuito del 74LS185 por medio del LUT que posee el simulador CircuitVerse:

Después lo organizamos según el datasheet para obtener un convertidor de binario a BCD de 7 bits

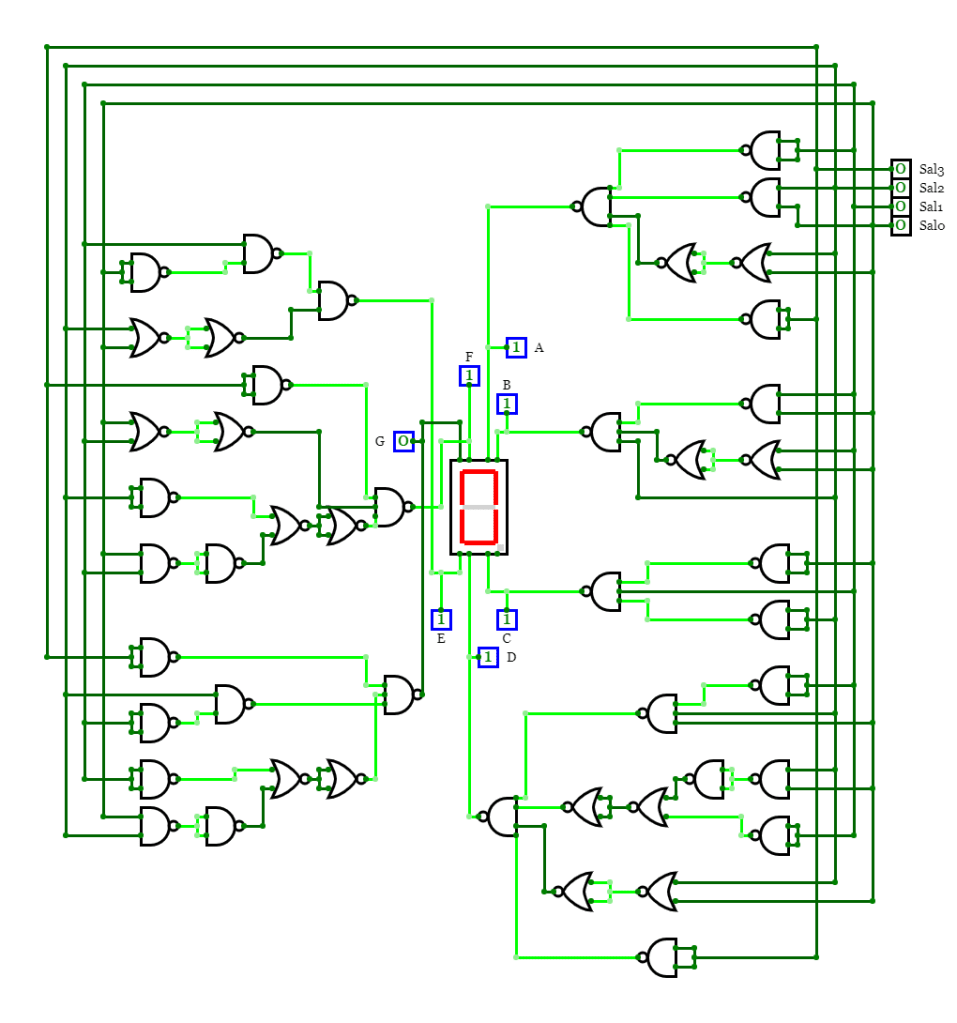

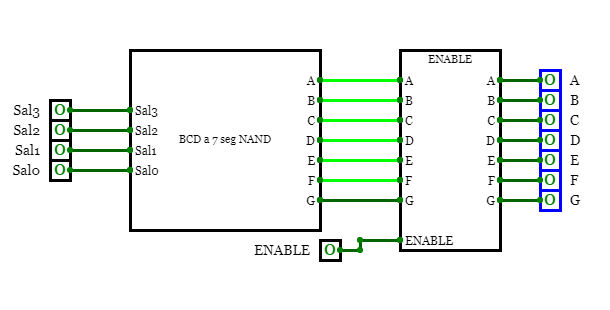

Después haremos un decodificador de BCD a 7 segmentos con puertas NAND y NOR y un ENABLE para poder variar la visualización por medio del contador de 2 bits:

Después añadimos el ENABLE:

Análisis de Resultados:

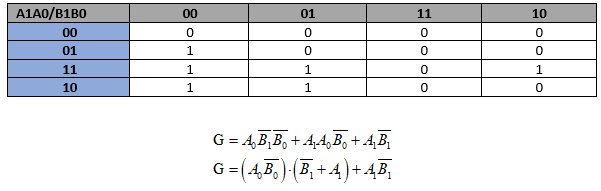

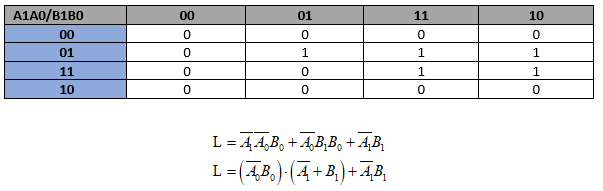

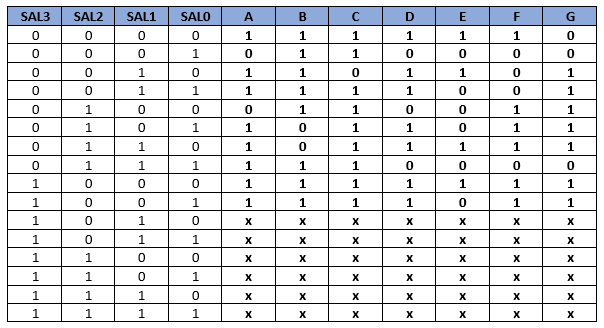

Observamos primero la creación de la tabla de verdad del comparador de 2 bits:

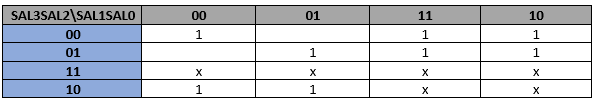

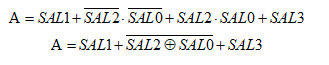

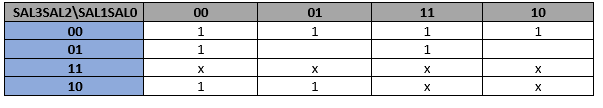

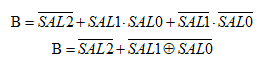

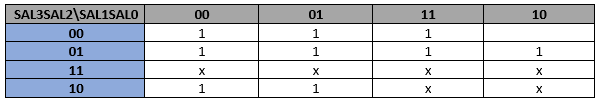

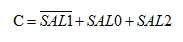

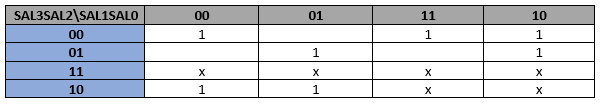

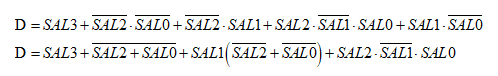

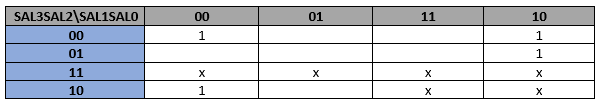

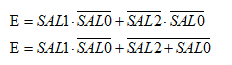

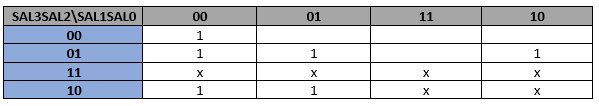

Luego por medio de Mapas de Karnaugh hallamos la ecuación para cada salida:

Para A > B:

Para A < B:

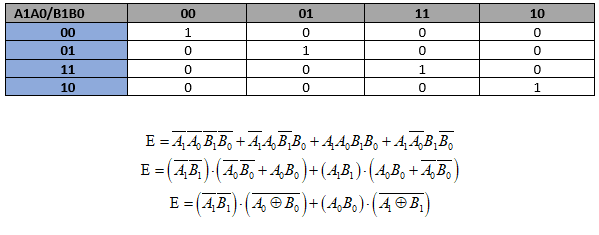

Para A = B:

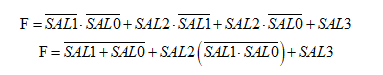

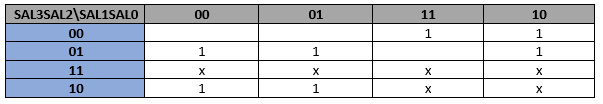

Hacemos la tabla de verdad del multiplexor de 2 a 1:

Para poder hacer la operación resta a partir de un sumador se hará este proceso por medio del complemento a 2, por lo que el circuito que realice dicha acción tendrá que hacer lo siguiente:

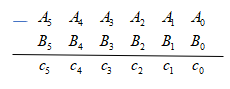

La operación resta:

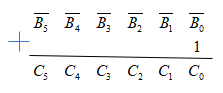

Ahora lo que haremos sera negar el numero B y sumarle 1:

Dándonos como resultado un nuevo número el cual sumaremos con el número A y de este modo realizaremos la operación resta

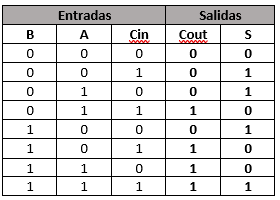

Por lo que realizaremos un circuito el cual al estar en 1 lo que haga sea negar el número y sumarle 1 para al final sumarlo con el otro número de 6 bits y de esta manera tendremos como resultado la resta. Después construiremos la tabla de verdad del sumador completo de 1 bit:

Ahora por medio de la tabla de verdad del 74LS185 diseñaremos su circuito con el LUT del simulador

De esta manera ya solo queda poder visualizar en el display por lo que a partir de la tabla de verdad del decodificador de BCD a 7 segmentos hallaremos sus ecuaciones por medio de Mapas de Karnaugh

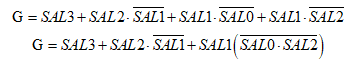

Por medio de Mapas de Karnaugh hallamos las ecuaciones de salida:

Segmento A:

Segmento B:

Segmento C:

Figura 32: Mapa de Karnaugh segmento C

Segmento D:

Segmento E:

Segmento F:

Segmento G:

Conclusiones:

– Aprender a usar el LUT que viene por defecto en el simulador CircuitVerse al igual que observar lo fácil que es por medio de una tabla de verdad diseñar un circuito un tanto complejo de una manera muy rápida y eficaz.

– Observar que las memorias latch SR son muy útiles para guardar datos de forma muy rápida y fácil de entender sin necesidad de un circuito complejo.

-Aprender acerca del sumador/restador al igual que entender la forma de restar por medio del método de complemento a 2 y aplicar también para números negativos.