Treceava Práctica

Introducción:

Para esta doceava práctica se usó la interfaz de Psoc con su respectiva tarjeta de desarrollo dada por el docente. En esta práctica se implementa el decodificador de binario a 7 segmentos que se viene utilizando con el uso de compuertas y se hará una comparativa al hacer este decodificador por medio del uso del lenguaje de descripción de hardware (HDL) Verilog.

Verilog:

es un lenguaje de descripción de hardware (HDL) utilizado para modelar sistemas electrónicos . Se utiliza más comúnmente en el diseño y verificación de circuitos digitales en el nivel de abstracción de transferencia de registro . También se utiliza en la verificación de circuitos analógicos y circuitos de señal mixta , así como en el diseño de circuitos genéticos .

Metodología:

Materiales:

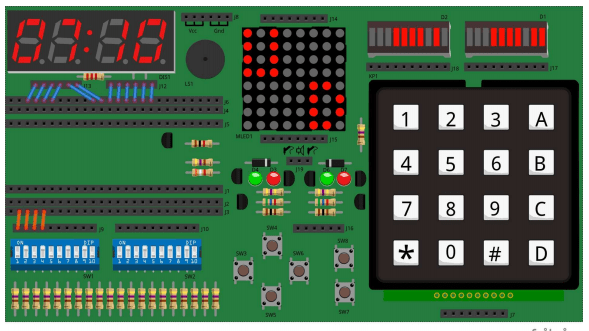

-Psoc-5lp.

-Jumpers para conexiones.

-4 entradas.

-1 display de 7 segmentos.

-1 decodificador de binario a 7 segmentos con compuertas logicas.

-1 decodificador de binario a 7 segmentos con Verilog.

Procedimiento:

Conexiones en la tarjeta de desarrollo:

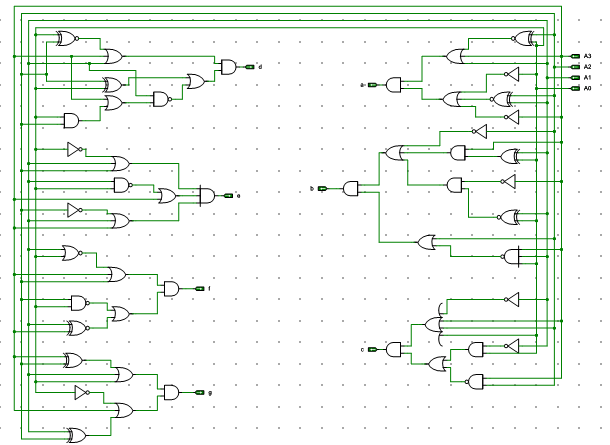

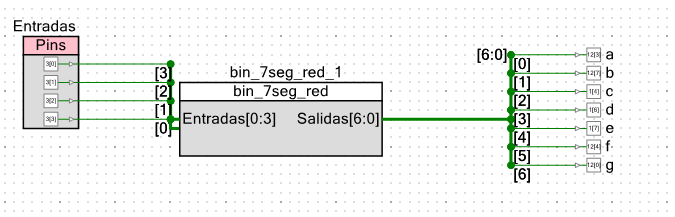

Para el diseño de este circuito hacemos uso del decodificador de binario a 7 segmentos hecho con compuertas logicas creado para practicas anteriores

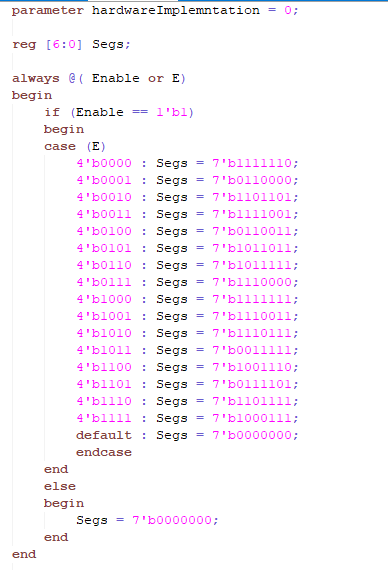

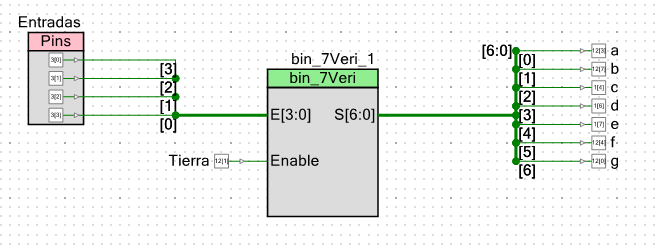

Después diseñamos el decodificador de binario a 7 segmentos a partir de Verilog:

Primero vamos seleccionar la opción «generate verilog» , se creará un nuevo archivo en formato «.V» en el cual ya estarán definidas las terminales del símbolo creado anteriormente y con un espacio disponible para describir el componente que deseamos implementar. Las descripciones de software pueden hacerse de manera estructural, funcional o comportamental,para este caso se ha optado por implementarlo de manera comportamental, pero puede realizarse la descripción de cualquiera de la tres maneras,esto esta a disposición del diseñador. Al momento de diseñarlo esto lleva su respectiva estructura.

Describimos el componente de la siguiente manera nombrando las entradas y salidas:

Después diseñamos la lista de sensibilidad o cláusula always la cual describe si nuestro circuito es sensible a cambios en las entradas. Después de esto va el desarrollo o procedimiento lógico de nuestro circuito. En este caso hicimos uso del comando case para el diseño del circuito.

Se genera un caso donde se disponen todas los casos posibles que pueden presentar las entradas junto con su respectiva salida de bits explicita.De esta manera queda implementado el componente y se puede probar.

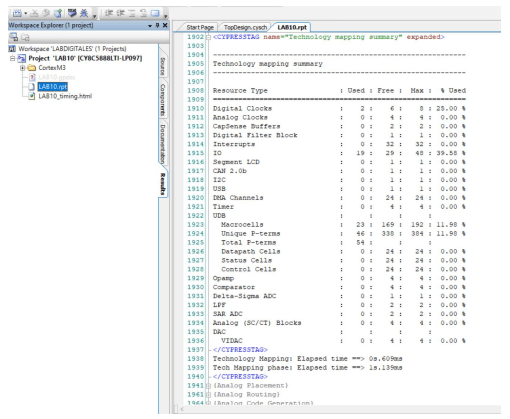

Ahora observamos el consumo de datos tanto en Verilog como con compuertas logicas:

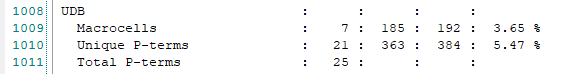

Con compuertas logicas:

Observamos el consumo de recursos:

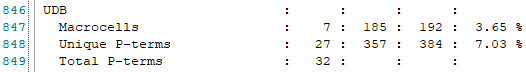

Con Verilog:

Observamos el consumo de recursos:

Conclusiones:

-Observar que al realizar el mismo circuito con la misma funcionalidad como en el caso del decodificador de binario a 7 segmentos podemos observar que los recursos consumidos son menores cuando se realiza el circuito por medio de compuertas lógicas que por medio del uso de Verilog.

-Notar que aunque en el diseño del circuito por medio de Verilog es más sencillo que por compuertas lógicas se nota un gran beneficio al realizar ciertos circuitos y teniendo en cuenta que el consumo de recursos es mayor que por compuertas pero no excesivamente mayor por lo que si nuestro circuito aun dispone de recursos para usar puede ser más viable generar el circuito por Verilog.